DVB-S Modulator IP Core Specification

| Release<br>Information | Name                   | DVB-S Modulator IP Core |

|------------------------|------------------------|-------------------------|

|                        | Version                | 3.0                     |

|                        | Build date             | 2017.11                 |

|                        | Ordering code          | ip-dvbs-modulator       |

|                        | Specification revision | r1884                   |

Features The IP core is full-featured digital DVB-S modulator and is fully compatible with this standard:

• ETSI EN 300 421 (v1.1.2)

License License:

• Netlist for One FPGA Family or Full Source Code (Verilog, SDC/XDC)

• Perpetual

- Without Quantitative Restrictions

- Worldwide

- Royalty-free

- Free Remote Technical Support for 1 Year

Deliverables

The DVB-S Modulator IP Core includes:

- EDIF/NGC/QXP/VQM netlist for Xilinx Vivado/ISE, Intel (Altera) Quartus, Lattice Diamond or Microsemi (Actel) Libero SoC

- IP Core testbench scripts

- Design examples for Xilinx, Intel (Altera), Lattice, and Microsemi (Actel) evaluation boards

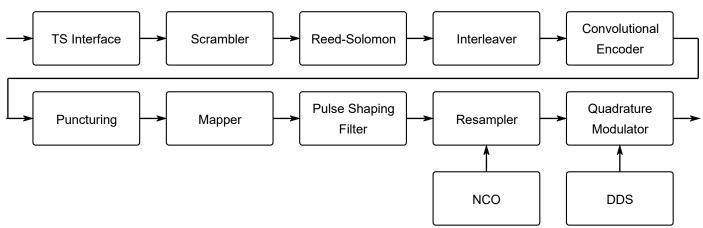

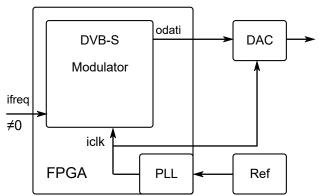

#### IP Core Structure Figure 1 shows the DVB-S Modulator IP Core block diagram.

Figure 1. The DVB-S Modulator IP Core block diagram

# Port Map

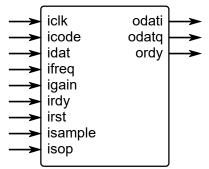

Figure 2 shows a graphic symbol, and Table 1 describes the ports of the DVB-S Modulator IP Core.

| Figure 2. The DVB-S Modulator port map | Figure 2. | The DVB-S Modulator | port map |

|----------------------------------------|-----------|---------------------|----------|

|----------------------------------------|-----------|---------------------|----------|

| Table 1. The DVB-S Modulator port map description |       |                                                                                |

|---------------------------------------------------|-------|--------------------------------------------------------------------------------|

| Port                                              | Width | Description                                                                    |

| iclk                                              | 1     | The main system clock. The IP<br>Core operates on the rising<br>edge of iclk.  |

| icode                                             | 3     | code rate:<br>0 - 1/2<br>1 - 2/3<br>2 - 3/4<br>3 - 5/6<br>4 - 7/8              |

| idat                                              | 8     | input (information) data                                                       |

| ifreq                                             | 32    | output intermediate frequency                                                  |

| igain                                             | W_DAC | output gain control                                                            |

| irdy                                              | 1     | Modulator output data request.                                                 |

| irst                                              | 1     | The IP Core synchronously reset when irst is asserted high.                    |

| isample                                           | 32    | bandwidth control (symbol<br>rate):<br>0.01% to 25% of iclk                    |

| isop                                              | 1     | input sync-word byte marker<br>(0x47 TS)                                       |

| odati                                             | W_DAC | modulator output at baseband<br>(I channel) or at an<br>intermediate frequency |

| odatq                                             | W_DAC | modulator output at baseband<br>(Q channel)                                    |

| ordy | 1 | ready to accept input data |

|------|---|----------------------------|

|------|---|----------------------------|

# IP Core Parameters

Table 2 describes the DVB-S Modulator IP Core parameters, which must be set before synthesis.

| Table 2. The DVB-S Modulator IP Core parameters description |                                                                                                                                                                           |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                   | Description                                                                                                                                                               |  |

| W_DAC                                                       | Width of output DAC symbols<br>(odati/odatq)<br>Increasing the width of<br>odati/odatq, increases the quality<br>of waveform but also increases<br>FPGA required resource |  |

Performance and Resource Utilization The values were obtained by automated characterization, using standard tool flow options and the floorplanning script delivered with the IP Core. The IP Core fully supports all Xilinx and Altera FPGA families, including Spartan, Zynq, Artix, Kintex, Virtex, Cyclone, Arria, MAX, Stratix. Table 3 summarizes the DVB-S Modulator IP Core measurement results.

| Table 3. The DVB-S Modulator performance |                                                                  |                                       |                               |                           |

|------------------------------------------|------------------------------------------------------------------|---------------------------------------|-------------------------------|---------------------------|

| IP Core                                  | FPGA type                                                        |                                       |                               |                           |

| parameters                               | Resource                                                         | Speed grade, maximal system frequency |                               |                           |

| W_DAC=16                                 | Altera Cyclone V 5CEFA7                                          |                                       |                               |                           |

|                                          | 2044 ALMs (4%)<br>5 M10K RAM blocks (1%)<br>12 DSP (18x18) (8%)  | -8, Fmax                              | -7, Fmax                      | -6, Fmax                  |

|                                          |                                                                  | 144.0 MHz<br>36.0 Msymb/s             | 170.0 MHz<br>42.5 Msymb/s     | 204.0 MHz<br>51.0 Msymb/s |

| W_DAC=16                                 | Xilinx Virtex-7 XC7VX330T                                        |                                       |                               |                           |

|                                          | 1163 Slices (3%)<br>3 18K RAM blocks (1%)<br>12 DSP (18x18) (2%) | -1, Fmax                              | -2, Fmax                      | -3, Fmax                  |

|                                          |                                                                  | 230.0 MHz<br>57.5 Msymb/s             | 297.0 MHz<br>74.25<br>Msymb/s | 310.0 MHz<br>77.5 Msymb/s |

# IP Core Interface Description

IP core has two ways of forming the output spectrum:

- Baseband (using odati and odatq), ifreq equal 0

- Intermediate frequency (using odati), ifreq not equal 0

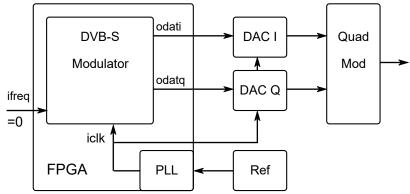

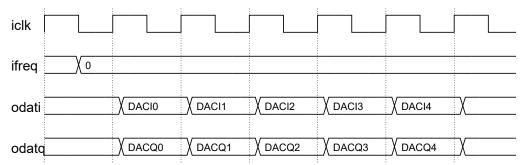

Digital-to-analog converters must operate synchronously with the DVB-S Modulator IP core. Figure 3 shows the DAC connection diagram for baseband mode and Figure 4 shows the timing diagram for this mode.

Figure 3. The DAC connection diagram for baseband mode.

Figure 4. The timing diagram for baseband mode.

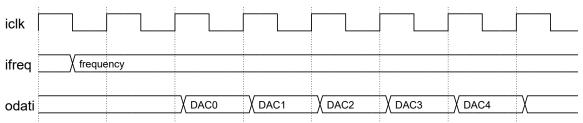

Figure 5 shows the DAC connection diagram for IF mode and Figure 6 shows the timing diagram for this mode. The output intermediate frequency port **ifreq** sets the central frequency for **odati** modulator output port.

Figure 5. The DAC connection diagram for IF mode.

Figure 6. The timing diagram for IF mode.

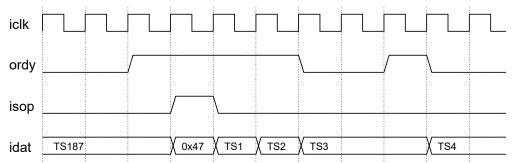

Figure 7 shows an example of the waveform of the input interface. Handshake port **ordy** controls input dataflow. Input data is read from the input **idat** only when **ordy** is equal to logical one ("1").

Figure 7. The timing diagram of the IP Core input interface.

Response time to changes in the output mode of the DVB-S modulator through **icode**, **isample** ports is not more than one thousand (1,000) DVB-S symbols. Proper forming of the DVB-S spectrum within one thousand (1,000) symbols after the configuration change is not guaranteed.

#### Upgrade and Technical Support Technical Support Free remote technical support is provided for 1 year and includes consultation via phone, E-mail and Skype. The maximum time for processing a request for technical support is 1 business day.

For up-to-date information on the IP Core visit this web page

https://www.modemica.com/

### Feedback Modemica OU

Sepapaja 6, Tallinn, 15551, Estonia

Tel.: +39-350-0080495

E-mail: info@modemica.com

Skype: fpgahelp

website: https://www.modemica.com

#### **Revision history**

| Version | Date       | Changes                                                                                                           |

|---------|------------|-------------------------------------------------------------------------------------------------------------------|

| 3.0     | 2017.11.14 | Added support for AD9361,<br>AD9363, AD9364, AD9371,<br>AD9375 and AD9789                                         |

| 2.0     | 2014.09.23 | Added support for Xilinx<br>Virtex-7, Kintex-7, Artix-7,<br>Altera Stratix V, Arria V,<br>Cyclone V, Lattice ECP5 |

| 1.1     | 2010.12.23 | Maintenance improvements                                                                                          |

| 1.0     | 2010.12.03 | Official release                                                                                                  |